Interface誌のFM3基板を使っているが、I2Cがうまくいかん。

一から書く気力がないので、Interface誌2012年7月号のドライバiic.c/hをそのままTOPPERS/ASPに載せ替え(というほどでもないか)をした。

割込が入らないとか何とかいう以前に、TDRレジスタに値を書き込んでMSS=1にしても、スタートコンディションになるだけでSDA/SCLが動かないのだ。

通信マクロの説明に従ってるのだが・・・

- TDR書き込み

- MSS=1

- BB=1になった

- ACT=1になった

- TRX=1になった

- FBT=1になった

- TDRE=0になった(すぐ1になるけど)

- SDA=Lになった

- ちょっとしてSCL=Lになった

ここまでいくのに、SDA/SCLともにLになりっぱなしなのだ・・・。

今回使っているのは、SOT1_2とSCL1_2。

FM3基板でいえば、CN2の31ピンと32ピン。

ch1は、FIFOなし。

プルアップ抵抗は、47kΩ。

動作クロックは変更していないので、144MHzでAPB1, APB2は72MHz。

APB1が40MHzを超えるならばノイズフィルタを設定した方がいいらしいが、出力だけなら気にしなくてもいいかと思い、設定してない。

DMAも使っていない。

情報はこれくらいか。

TDRに書き込む前は、TDRE=1なので、送信データレジスタへ書き込める条件は整っている。

MSS=1にする際は、同時にINTEとINTも1にしている。読み取ると、INTは0だけど、これは割込条件が整っていないから0なだけだろう(INTへの1書き込みは、意味がないのだな)。

割込が入らないのは、データを送信できていないから。

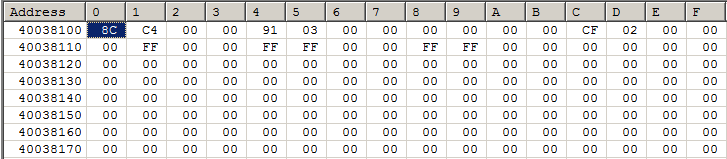

TDR書き込み直後のMFS関連のレジスタ値

- SMR : 0x8C

- IBCR : 0x00

- IBSR : 0x00

- SSR : 0x01

- BGR0 : 0xB3

- BGR1 : 0x00

- ISBA : 0x00

- ISMK : 0xFF

MSS=1書き込み直後

- SMR : 0x8C(MD=100/RIE=1/TIE=1)

- IBCR : 0xC4(MSS=1/ACT=1/INTE=1)

- IBSR : 0x91(FBT=1/TRX=1/BB=1)

- SSR : 0x03(TDRE=1/TBI=1)

- BGR0 : 0xB3

- BGR1 : 0x00

- ISBA : 0x00

- ISMK : 0xFF

このまま放置しても、レジスタ値に変化なしだ。

うーむ。

FBT=1のままってことは、まだ送信できていないと思っているのだろう。

TRX=1だから、送信ってことはわかってるし。

BB=1なので、送受信しようとはしているようだ。

TDREも0から1になっているので、シフトレジスタへ載ってるんだと思う。

ちなみにオリジナルは、RIEとTIEは0だ。

まあ、まだ割込が発生する以前の問題だから、あとで考えよう。

PZRレジスタでHiZにしてやらんといかんのか?とやってみたが、変わりなし。

なんか全然わからんぞ-。

メモ代わりに、MSS=1後のレジスタを載せておこう。。。

0 件のコメント:

コメントを投稿

コメントありがとうございます。

スパムかもしれない、と私が思ったら、

申し訳ないですが勝手に削除することもあります。

注: コメントを投稿できるのは、このブログのメンバーだけです。